Grade Distributions

Exam III, Final

Median = 7.9

Mean = 8.23

X

X X

X X X X

X X X X X

X X X X X

X X X X X

X X X X X X X X X

X X X X X X X X X X X X

_________X_X_X_X_X_X_X_X_X_X_X_X___X__________

0 . 2 . 4 . 6 . 8 . 10. 12. 14. 16. 18. 20

Exams I II III

Median = 18.1

Mean = 18.69

X

X X X X

X X X X X X X

X X X X X X X X X X

X X X X X X X X X X X X X

_____X_X_X_X_X_X_X_X_X_X_X_X_X_X_____X___X_X_X___X_X___X______

8 . 10. 12. 14. 16. 18. 20. 22. 24. 26. 28. 30. 32. 34. 36

10. 12. 14. 16. 18. 20

Programming Assignments 1 to 6

Median = 15.1 X X X X

Mean = 15.93 X X X X X X X

X X X X X X X X X

X X X X X X X X X X X X X X X

_____X___X_X_X_X_X_X_X_X_X_X_X_X_X_X_X_____X_X_______X___X_X__

2 . 4 . 6 . 8 . 10. 12. 14. 16. 18. 20. 22. 24. 26. 28. 30

Weekly Quizzes (top 10 out of 12 scores)

X

Median = 29.0 X

Mean = 27.98 X

X

X X

X X

X X

X X

X X X

X X X

X X X X

X X X X

X X X X X

X X X X X X X

X X X X X X X X

___________________X___X_____X_X_X_X_X_X_X_X__

10. 12. 14. 16. 18. 20. 22. 24. 26. 28. 30

Total of Exams, Programming and Quizzes

Median = 61.6

Mean = 62.60

X

X X X X

X X X X X X X

X X X X X X X X X

X X X X X X X X X X X X X

_____X___X_X_X_X_X_X_X_X_X_X_X_X_X_X_X_______X_X_X_X_X_X______

40. 44. 48. 52. 56. 60. 64. 68. 72. 76. 80. 84. 88. 92. 96

D + - C + - B + - A +

Solutions and Commentary

This exam is open book, open-notes, closed neighbor, no electronics!

This exam is worth 20 points. Each question is worth 0.5 points, so allocate

about 2.5 minutes of your time per question.

8-bit FP format

| 07 | 06 | 05 | 04

| 03 | 02 | 01 | 00

|

|

| S

| exp

| mant

|

The floating-point format at right was discussed in class Friday.

It works like the IEEE format, with a hidden bit, exponent values 111

and 000 set aside for NaN and non-normalized, and a bias of 3 for

other exponents.

_MOVE__ _R4,R3_

_SR____ _R4,4__

_TRUNC_ _R4,3__

_______ _______

TESTR R4

BZS EDONE

CMPI R4,SHORTNAN

BZS ENAN

ADDI R4,IEEEBIAS-SHORTBIAS

BR EDONE

ENAN:

LIL R4,IEEENAN

EDONE:

|

- Given that R3 holds a number in this format,

write SMAL Hawk code in the space to the right to extract the

exponent into the low bits of R4.

12 left this blank, 23 gave wrong answers, 6 earned full credit.

The most common error was to use SL R4,1 to clear the sign,

as if R4 was an 8-bit register;

other common errors included transposed registers,

and forgetting to clear the sign.

The code given to the right starting with TESTR

converts the 3-bit exponent in the low bits of

R4 from this short format to an 8-bit IEEE format exponent.

What is the correct definition of each constant?

- SHORTNAN = ___7______________

5 left this blank, 26 gave wrong answers, 23 made no errors.

- SHORTBIAS = ___3______________

6 left this blank, 30 gave wrong answers, 19 made no errors.

A very few got partial credit for giving 4.

- IEEEBIAS = ___127____________

5 left this blank, 32 gave wrong answers, 14 made no errors.

A very few got partial credit for giving 128 or (for even less credit) 31.

- IEEENAN = ___255____________

4 left this blank, 31 gave wrong answers, 19 made no errors.

A very few got partial credit for giving 63.

_SL____ _R4,11_

_SL____ _R4,12_

_______ _______

|

- In the space to the right, add instructions to move the exponent

in the low bits of R4 into the correct position in R4

for an IEEE-format floating-point number

10 left this blank, 27 gave wrong answers, 2 made no errors.

The most common error (for partial credit) was to try to use a shift

count greater than 16.

A few shifted the wrong direction or had total shift counts that were wrong.

- Given your solution to problem 1, is the TESTR

instruction above unneeded? (Yes) or No

10 left this blank, 22 gave wrong answers, 21 made no errors.

Grading this was made difficult because of the need to use the context

from probem 1, but for those who left problem 1 blank, the TESTR

instruction was definitely needed.

- In the Hawk code given above to the right

from TESTR to LIL, some of the instructions

are short and some are long. List the long ones below:

________CMPI___ADDI___LIL________________________

None left this blank, 21 made no errors.

Over 10 missed LIL, over 5 missed ADDI, exactly 5

missed CMPI. A few each included branch or TESTR

instructions.

- In the Hawk code from TESTR to LIL,

some of the instructions are actually variations on what same Hawk instruction?

________LEACC____________________________________

1 left this blank, 39 gave wrong answers, 5 made no errors.

A few got partial credit for BR because a case can be made for

BZS and BR all being variant branch instructions.

The most popular Completely wrong answer was CMP.

- In base 2, what halfword does the assembler create from the

BR EDONE instruction?

| 0 | 0 | 0 | 0

| 0 | 0 | 1 | 0

| 0 | 0 | 0 | 0

| 0 | 0 | 0 | 0

|

12 left this blank, 15 gave wrong answers, 6 made no errors.

The most common small error was to switch the byte order.

The other common errors were incorrect branch displacements off a small amount.

FUNC:

TRUNC R4,4

LOAD R5,STUFF

ADDSL R4,R5,8

STORES R4,R2

JUMPS R2

ALIGN 4

STUFF:

TRUNC R3,16

JUMPS R1

|

The function to the right entirely conforms to the standard Hawk calling

sequence conventions. It has been tested; it works.

-

If FUNC is called with R4 set to FFFFFFFF16,

what value does TRUNC R4,4 leave in R4?

(Answer in hex)

6 left this blank, 19 gave wrong answers, 16 made no errors.

The most common wrong answer was 0000FFFF, for less than half credit.

- What addressing mode is used by LOAD R5,STUFF?

_____PC_relative_________________________________

2 left this blank, 12 gave wrong answers, 43 made no errors.

A few earned partial credit by saying indexed addressing, because

on the Hawk, PC-relative addressing for long memory-reference instructions

is a variant of indexed mode.

- What value does LOAD R5,STUFF leave in R5?

(Answer in hex)

6 left this blank, 39 gave wrong answers, none made no errors.

A fair number earned partial credit with errors in scattered hex digits of

the code, but there were no obvious patterns to the errors.

- Why is ALIGN needed?

____To_assure_that_the_next_instructions_share_a_word_________

None left this blank, 44 gave wrong answers, 5 made no errors.

Many made unclear assertions about what instructions would be in the aligned

word. No credit was given for those who simply described what ALIGN

does without saying why it mattered.

- Where does the STORES instruction store the

modified data loaded from STUFF?

____In_the_activation_record_of_FUNC_____________

1 left this blank, 23 gave wrong answers, 16 made no errors.

Over 10 earned partial credit with R2, and a few got credit for

saying the RETAD field, although FUNC never stores its

return address in its activation record.

- How big is the activation record of FUNC in bytes?

__4_bytes______

None left this blank, 28 gave wrong answers, 17 made no errors.

Over 10 said 8 bytes; this was given partial credit as an off-by-one error,

since 8 bytes is two words. No credit was given for wild numbers such as

16 or even 64 bytes.

- If FUNC is called with R3 = -1

and R4 = 5, what does it return in R3?

(Answer in hex)

13 left this blank, 42 gave wrong answers, 1 made no errors.

It is very clear that few students had any clue what FUNC does.

- Why might this code fail to work on a machine with separate

I-cache and D-cache?

____The_CPU_might_fetch_a_cached_instruction_____

____instead_of_the_one_saved_by_the_STORES_______

12 left this blank, 41 gave wrong answers, none made no errors.

A few earned partial credit for saying that there could be a cache coherency

problem.

- Which instruction in the above code would cause a trap if this code

was run on a Sparrowhawk processor?

____LOAD_________________________________________

3 left this blank, 23 gave wrong answers, 28 made no errors.

Strange wrong answers included ADDSL and JUMPS.

; activation record

;RA = 0

I = 4

A = 8

ARSIZE = 24

|

Consider writing code for a function using the activation record

described to the right, where A is a local array of 4 words.

- Write Hawk code to load the value of I into R3.

________LOAD____R3,R2,I__________________________

None left this blank, 8 gave wrong answers, 24 made no errors.

The most common small error, made by over 15, was to omit R2;

over 5 each omitted I or used the wrong load instruction.

- Write Hawk code to load the address of A into R4.

________LEA_____R4,R2,A__________________________

1 left this blank, 7 gave wrong answers, 32 made no errors.

The most common small error, made by over 10, was to omit I;

over 5 used the wrong load instruction.

- Given the value of I in R3 and

the address of A in R4, write Hawk code to compute

the address of A[I] in R3

________ADDSL___R3,R4,2__________________________

3 left this blank, 28 gave wrong answers, 20 made no errors.

A few threw in extra instructions or used the wrong shift count.

- Given the address of A[I] in R3, write Hawk code

to do A[I] = A[I] + 1.

________LOADS___R4,R3____________________________

________ADDSI___R4,1_____________________________

________STORES__R4,R3____________________________

6 left this blank, 21 gave wrong answers, 13 made no errors.

The most common small error, made by over 10, was to forget to store the

result back in memory. A few forgot to load the value before incrementing,

or managed to swap the roles of R3 and whatever temporary register

they used.

The next group of questions concerns calls to subroutines, functions or

methods. Assume that pushing and popping the activation record is taken care

of outside the code you write here.

__JSR___ __R1,SUB1_______

________ ________________

__LIL___ __R1,SUB2_______

__JSRS__ __R1,R1_________

__LOAD__ __R1,R3,METHOD__

__JSRS__ __R1,R1_________

|

- Consider a source file containing the label SUB1 somewhere

within it.

Write Hawk code to call SUB1 in the space to the right.

2 left this blank, 19 gave wrong answers, 12 made no errors.

A small penalty was given to over 10 who gave LIL/JSRS sequences

that worked but were inefficient. Larger penalties were given for

plausible wrong opcodes or using the wrong register for the return address.

- Consider a source file containing the definition EXT SUB2.

Write Hawk code to call SUB2 in the space to the right.

4 left this blank, 22 gave wrong answers, 19 made no errors.

Over 5 were penalized for using the wrong opcode or the wrong register for

the return address.

- Consider a header file class.h that defines a polymorphic

class, where one of the methods of every object in that class is

METHOD. Assume that R3 points to an object in that class.

Write Hawk code to call METHOD in the space to the right.

7 left this blank, 22 gave wrong answers, 14 made no errors.

A few got partial credit, but there was no pattern to the errors.

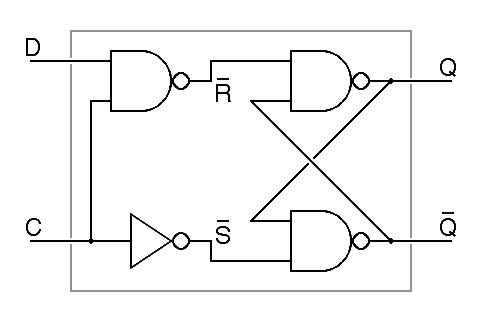

- For the flipflop at right, what value of C causes Q to equal the D input?

___1___________________

None left this blank, 28 gave wrong answers, 28 made no errors.

- The label Q here is poorly chosen.

For what value of the input C is Q ≠ Q?

___0___________________

None left this blank, 30 gave wrong answers, 25 made no errors.

- When the C input allows this flipflop to remember, ingnoring its D input,

how are Q and Q related?

___Their_values_will_be_opposites________________

5 left this blank, 30 gave wrong answers, 17 made no errors.

A few got partial credit for answers such as Q implies not

Q but saying nothing about what not Q implies.

L1: LOAD R3,R2,A

L2: LOAD R4,R2,B

L3: STORE R4,R2,A

L4: ADD R3,R3,R4

L5: STORE R3,R2,B

|

Consider executing the instructions to the right on a pipelined machine.

- Give the labels of the instructions that depend on a result

of the immediately preceeding instruction.

_____L3__L5______________________________________

None left this blank, 8 gave wrong answers, 19 made no errors.

Among those earning partial credit, over 20 listed L4,

over 10 omitted L3, and over 5 omitted L5.

- Give a better order that would improve pipelined execution.

__L1__L2__L4__L3__L5___or___L2__L1__L3__L4__L5___

1 left this blank, 30 gave wrong answers, 15 made no errors.

The first answer above was by far the most popular;

over 5 gave orders that did not break the computation but contained even

more dependencies than the original.

78 LSPUSH:

79 LOAD R5,R3,HEAD

80 LIS R3,OBJSIZE

81 LIL R1,MALLOC

82 JSRS R1,R1

83 CMPI R1,0

84 BEQ THROW

85 MOVE R6,R3

86 STORE R4,R6,DATA

87 STORE R5,R6,NEXT

88 STORE R6,R3,HEAD

89 JUMPS R1

|

Several students wrote code like that to the right for MP5 or MP6:

- The code goes into an infinite loop that ends at line 89.

Which line is the top of the loop?

___83____________

None left this blank, 20 gave wrong answers, 19 made no errors.

Off by one errors earned partial credit; over 10 gave 82, over 5 gave 84.

- To prevent this loop, new lines of code must be added

before line 81 and after line 82. What are they?

_____LOADS___R1,R2___or___ADDI___R2,R2,ARSIZE____

_____STORES__R1,R2___or___ADDI___R2,R2,-ARSIZE___

7 left this blank, 25 gave wrong answers, 15 made no errors.

Either answer above was acceptable, but in fact, both answers are needed to

repair the code.

- This code contains a second error. What registers did the programmer

forget to save in the activiton record before calling MALLOC?

_____R1___R3___R4___R5___________________________

1 left this blank, 19 gave wrong answers, 1 made no errors.

Among those earning partial credit,

over 25 omitted R1, over 20 omitted R2, over 5 omitted

R4 and a few omitte R3.

- What short instruction could replace the instruction on

line 83?

_____TESTR___R1__________________________________

1 left this blank, 22 gave wrong answers, 38 made no errors.

Here is an actual bus trap error message from a solution to MP6

/------------------CPU------------------\ /----MEMORY----\

PC: 00000000 R8: 00000000 FFFFFC: --

PSW: 0000FF01 R1: 000010F6 R9: 00000000 FFFFFE: --

NZVC: 0 0 0 1 R2: 0001009C RA: 00000000 ->000000: LIL R2,#010074

R3: 000007C6 RB: 00000000 000004: JSR R1,#00032C

R4: 00000000 RC: 00000000 000008: LIL R1,#00108C

R5: 0001FF88 RD: 0001FFC4 00000C: JSRS R1,R1

R6: 000104A0 RE: 0001FF88 00000E: BR #000000

R7: 0001FFC0 RF: 0001FF4C 000010: CPUSET R2,#3

**HALTED** r(run) s(step) q(quit) ?(help)

Bus Trap. Trap PC = #00001072

Trap MA = #000007C8 invalid addr

Here is an anonymized fragment of the assembly listing for the code that caused this trap:

+00000058: F5 23 000C 76 STORE R5,R3,HEAD

+0000005C: F6 A5 77 STORES R6,R5

+0000005E: F0 B1 78 JUMPS R1

79

80 ;================

81 ; LSPOP

82 LSPOP:

+00000060: F5 73 0000 83 LEA R5,R3,NODVAL

+00000064: F7 73 0038 84 LEA R7,R3,OBJSIZ

+00000068: 07 07 85 BLEU THROW

+0000006A: F5 23 000C 86 STORE R5,R3,HEAD

+0000006E: E3 +000000 87 LIL R3,FREE

+00000072: F5 23 0004 88 STORE R5,R3,NODPTR

+00000076: F0 B1 89 JUMPS R1

90

91 THROW:

+00000078: E3 +000000 92 LIL R3,STACKEXCEPT

+0000007C: F1 D3 93 LOADS R1,R3

+0000007E: F2 51 0008 94 LOAD R2,R1,EXOLD

- Give the line number (not the memory address) of the instruction that

caused the trap.

_____88__________________________________________

None left this blank, 6 gave wrong answers, 41 made no errors.

- What register contained an address that caused this bus trap?

_____R3__________________________________________

None left this blank, 3 gave wrong answers, 47 made no errors.

- Give the line number (not memory address) of the instruction that

loaded the address into the register you identified in question 37?

_____87__________________________________________

None left this blank, 28 gave wrong answers, 36 made no errors.

A few gave 83, even fewer gave 84.

- The instruction you identified in question 38

loaded the wrong register. What register should it have loaded?

_____R1__________________________________________

None left this blank, 28 gave wrong answers, 29 made no errors.

A few each listed R2, R4, R5, R6 or

R7, earning no credit.

- There is a missing instruction after the instruction you

identified in question 38. What is it?

_____JSRS____R1,R1_______________________________

2 left this blank, 23 gave wrong answers, 21 made no errors.

A few earned partial credit for JSRS without giving the registers.

The most popular wrong answer was LOADS, which does not seem related

to an understanding of what caused the trap.

There are many more errors in the above code, but they are not the subject

of this exam. Many of them parallel errors seen on the previous code example.