| inputs | outputs | |||||

| ai | bi | ci | pi | gi | si | |

| 0 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 0 | 0 | 1 | |

| 0 | 1 | 0 | 1 | 0 | 1 | |

| 0 | 1 | 1 | 1 | 0 | 0 | |

| 1 | 0 | 0 | 1 | 0 | 1 | |

| 1 | 0 | 1 | 1 | 0 | 0 | |

| 1 | 1 | 0 | 1 | 1 | 0 | |

| 1 | 1 | 1 | 1 | 1 | 1 | |

a) Complete the truth table for this adder in the blanks to the right (2 points)

The answers are shown in italics in the table. Many got the generate entry correct, but the propogate entry proved more difficult. In general, a carry will propogate from carry in to carry out if either the a or b inputs is one.

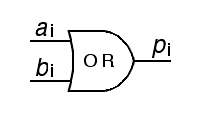

b) Give the logic diagram for pi as a function of ai, bi and ci. (2 points)

1 got this exactly, and half the class were corect in terms of the answer the student gave to part a). Of the remainder, many were partially correct.

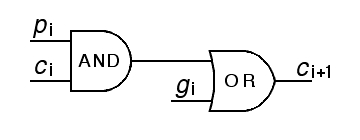

c) Give a logic diagram for the ci+1 output as a function of pi, gi and ci. (2 points)

7 did well here, mostly by deriving the correct logic from the original English description. As many produced the correct values of carry out, although apparently more by accident than anything else, and as many more had significant errors. About a quarter of the class earned no credit.

| FF100004 |

| Keyboard status and control register | ||||||||||||||||

| IE = interrupt enable (control) | ||||||||||||||||||

| ER = error (status) | ||||||||||||||||||

| RD = input data ready (status) | ||||||||||||||||||

a) Write Hawk code for a polling loop that blocks until the RD bit is set. Use hex constants for the memory address and bit number. (2 points)

LIW R4,#FF100004

LP: LOADS R3,R4

TSTB R3,7

BCR LP

17 did well here. The most common error was to fail to load the correct address. The second most common error was to fail to use the correct memory addressing instruction.

b) Write Hawk code to set the IE bit. Use hex constants for the memory address and bit number. (1 point)

LIW R4,#FF100004

LIS R3,#80

STORES R3,R4

Only 2 did well here. Many stored something in the wrong place in memory, a few wrote code to toggle the bit, and a remarkable number copied code from part a) that incorporated some kind of polling loop.

c) Even if the IE bit is set to one and a key has been pressed, interrupts may still be prevented. What other status bit or bits control whether the keyboard (and other devices) will be able to cause an interrupt? (1 point)

The top 4 bits of the processor status word, the level field, are used on the Hawk as a global interrupt enable field.

About 3 gave this answer, and one more simply commented on a global interrupt enable bit for partial credit. It is true that interrupts will not occur if the ready bit is not set, and many gave this answer, but a little care in reading the question will show that the ready bit is assumed to be set ("even if a key has been pressed"). The error bit does not inhibit interrupts! This was the most common entirely wrong answer given.

of 32 words. In the event that access to AA requires a pointer, call it PAA.

a) Write SMAL Hawk assembly code to create AA and (if necessary) PAA. (1 point)

COMMON AA,128

PAA: W AA

12 did well here, while almost as many had trouble with the size of the common block but were otherwise correct. The block size is given in bytes, while the array was described as being 32 words!

b) Write SMAL Hawk assembly code to load the address of AA into R3. (1 point)

LOAD R3,PAA

13 did well here. Typical errors involved one too many or one too few levels of indirection (loading the address of PAA with LEA, or loading the contents of the first location in AA).

c) Write SMAL Hawk assembly code to set all 32 words of AA to zero, given that you have loaded the address of AA into R3. (2 points)

LIS R4,32 ; load loop counter

L: STORES R0,R3 ; clear one location in array

ADDSI R3,4 ; advance pointer to next location

ADDSI R4,-1 ; decrement count of locations remaining

BGT L ; iterate

3 did well here. The most common errors involved failure to advance the memory address by 4 for each word loaded; over 20 made this error. Miscounting the number of memory locations was also common, with over 10 making this error. Over 15 failed to properly store zero in some memory location.

a) Write plausable definitions for the identifiers LEFT, RIGHT and PUTVAL, likely to be found in the SMAL header file for the abstract tree-node class. These are identifiers are displacements into the class descriptor. (1 point)

LEFT = 0 RIGHT = 4 PUTVAL = 8

16 did well here. There was little partial credit. 12 had EXT directives and similar material, while the remainder had strange answers. Note that this question was closely tied to the final machine problem. Students who had studied the materials distributed for that assignment should have had an easy time here.

b) Write appropriate definitions for the identifiers associated with the activation record of a SMAL Hawk routine that does a recursive traversal of a binary tree created using these classes. Assume the usual parameter passing conventions for the Hawk. (1 point)

RA = 0 P = 4 ARSIZE = 8

15 did well here, not necessarily giving the most sensible local variables but at least giving something that passed the basic test as an appropriate definition of an activation record in assembly language, in the style used throughout the semester.

c) Write the code to do an in-order recursive traversal of this tree, assuming the activation record and class description structures outlined in parts a and b and assuming the usual calling conventions for the Hawk. (With no optimization and pure cookbook coding, this takes 21 instructions; comments are provided for the first third of the code to serve as a guide). (4 points)

TRAV: STORES R1,R2 ; save return address

STORE R3,R2,P ; save pointer to node

LOADS R1,R3 ; get pointer to class description

LOAD R1,R1,LEFT ; get pointer to LEFT method

ADDI R2,R2,ARSIZE ; push activation record

JSRS R1,R1 ; call LEFT method

ADDI R2,R2,-ARSIZE ; pop activation record

TEST R3

BZS NOLEFT ; if left pointer not null

ADDI R2,R2,ARSIZE

JSR R1,TRAV ; recursive call on left node

ADDI R2,R2,-ARSIZE

NOLEFT:

LOAD R3,R2,P

LOADS R1,R3

LOAD R1,R1,PUTVAL

ADDI R2,R2,ARSIZE

JSRS R1,R1 ; call p.putval()

ADDI R2,R2,-ARSIZE

LOAD R3,R2,P

LOADS R1,R3

LOAD R1,R1,RIGHT

ADDI R2,R2,ARSIZE

JSRS R1,R1 ; call p.right()

ADDI R2,R2,-ARSIZE

TEST R3

BZS NORIGHT ; if right pointer not null

ADDI R2,R2,ARSIZE

JSR R1,TRAV ; recursive call on right node

ADDI R2,R2,-ARSIZE

NORIGHT:

LOADS R1,R2

JUMPS R1 ; return

There were no fully correct answers. A fair number had the recursion scheme correct except for termination tests (there are two reasonable termination tests; the one given is compatible with the comments that were included in the exam, on the first 7 lines above). Several had no recursive calls, or attempted a fully iterative solution. Others had some traversal order other than inorder, typically trying to visit the node after visiting both children.