# Logic Design

# See Appendix B of your Textbook

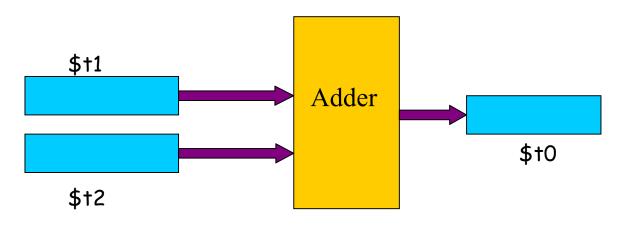

When you write add \$t0, \$t1, \$t2, you imagine something like this:

What kind of hardware can ADD two binary integers?

We need to learn about GATES and BOOLEAN ALGEBRA that are foundations of logic design.

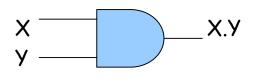

#### <u>AND gate</u>

| Х | У | Х.У |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

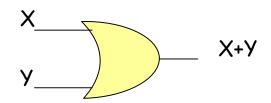

<u>OR gate</u>

| Х | У | Х+У |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

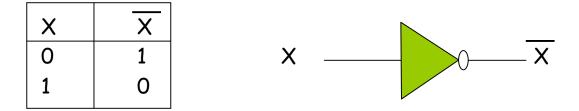

NOT gate

Typically, logical 1 = +3.5 volt, and logical 0 = 0 volt. Other representations are possible.

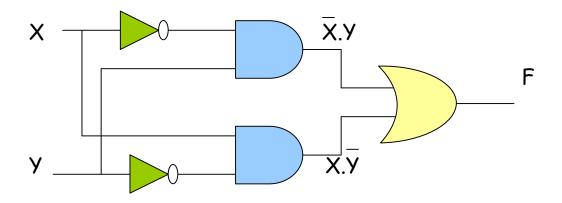

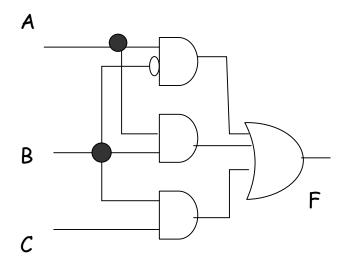

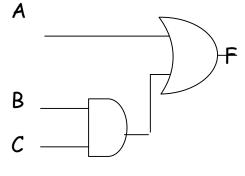

### Analysis of logical circuits

What is the value of F when X=0 and Y=1?

Draw a truth table.

| X | У | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

This is the exclusive or (XOR) function. In algebraic form  $F = \overline{X}.Y + X.\overline{Y}$

#### More practice

- 1. Let  $\overline{A}$ .B + A.C = 0. What are the values of A, B, C?

- 2. Let (A + B + C).(A + B + C) = 0. What are the possible values of A, B, C?

- Draw truth tables.

- Draw the logic circuits for the above two functions.

# Boolean Algebra

| A + 0 = A | A + A' = 1 |  |  |

|-----------|------------|--|--|

| A . 1 = A | A. A' = 0  |  |  |

$\begin{array}{c}

1 + A = 1 \\

0. A = 0

\end{array}$   $\begin{array}{c}

A + B = B + A \\

A \cdot B = B \cdot A

\end{array}$

A + (B + C) = (A + B) + CA. (B. C) = (A. B). C

$$A + A = A$$

$$A \cdot A = A$$

A. (B + C) = A.B + A.CA + B.C = (A+B). (A+C)Distributive Law

$\overline{\overrightarrow{A} \cdot \overrightarrow{B}} = \overline{\overrightarrow{A}} + \overline{\overrightarrow{B}}$   $\overline{\overrightarrow{A} + \overrightarrow{B}} = \overline{\overrightarrow{A} \cdot \overrightarrow{B}}$ De Morgan's theorem

#### De Morgan's theorem

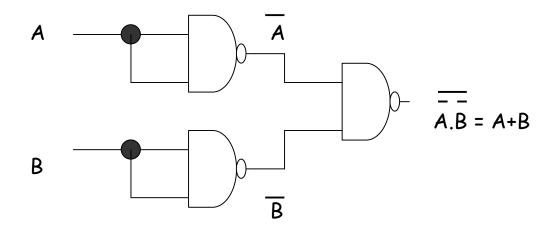

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

$$\overline{A + B} = \overline{A} \cdot \overline{B}$$

Verify it using truth tables. Similarly,

These can be generalized to more than two variables: to

$$\overline{A. B. C} = \overline{A + B + C}$$

$$\overline{A + B + C} = \overline{A \cdot B \cdot C}$$

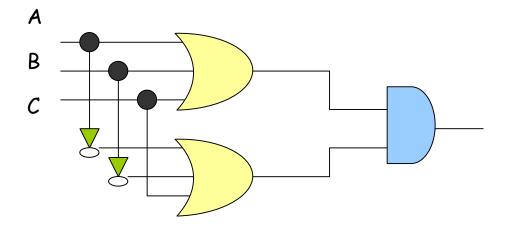

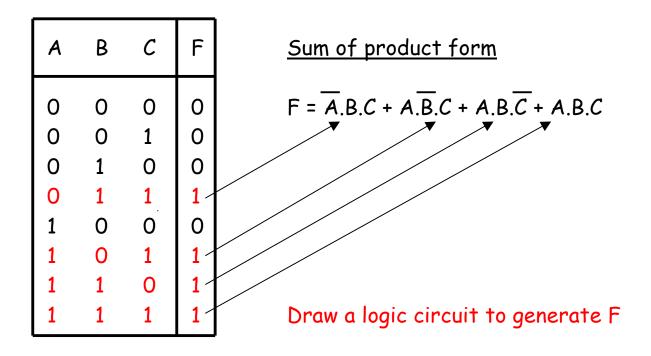

### Synthesis of logic circuits

Many problems of logic design can be specified using a truth table. Give such a table, can you design the logic circuit?

Design a logic circuit with three inputs A, B, C and one output F such that F=1 only when a majority of the inputs is equal to 1.

### Simplification of Boolean functions

Using the theorems of Boolean Algebra, the algebraic forms of functions can often be simplified, which leads to simpler (and cheaper) implementations.

#### Example 1

| F | = | $\overline{A.B}$ + $A.B$ + $B.C$ |

|---|---|----------------------------------|

|   | = | A. (B + B) + B.C                 |

|   | = | A.1 + B.C                        |

|   | = | A + B.C                          |

How many gates do you save from this simplification?

### Example 2

$$F = \overline{A.B.C + A.B.C + A.B.C} + A.B.C$$

$$= \overline{A.B.C + A.B.C + A.B.C + A.B.C + A.B.C + A.B.C}$$

$$= (\overline{A.B.C + A.B.C}) + (\overline{A.B.C + A.B.C}) + (\overline{A.B.C + A.B.C})$$

$$= (\overline{A} + A). B.C + (\overline{B} + B). C.A + (\overline{C} + C). A.B$$

$$= B.C + C.A + A.B$$

- Example 3 Show that A + A.B = A

- A + AB

- = A.1 + A.B

- = A. (1 + B)

- = A.1

- = A

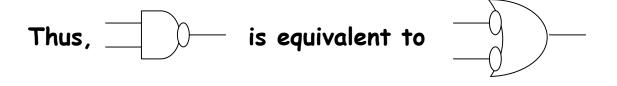

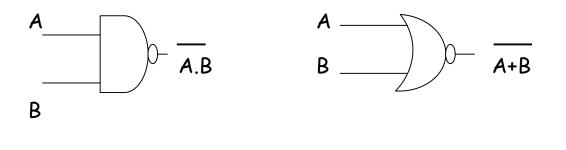

Other types of gates

NAND gate

NOR gate

Be familiar with the truth tables of these gates.

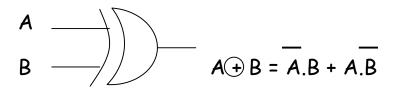

Exclusive OR (XOR) gate

#### NAND and NOR are universal gates

Any function can be implemented using only NAND or only NOR gates. How can we prove this?

(Proof for NAND gates) Any boolean function can be implemented using AND, OR and NOT gates. So if AND, OR and NOT gates can be implemented using NAND gates only, then we prove our point.

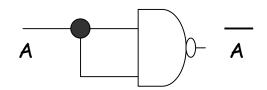

1. Implement NOT using NAND

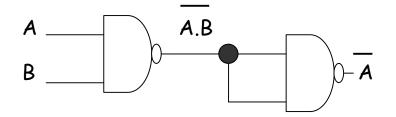

#### 2. Implementation of AND using NAND

#### 3. Implementation of OR using NAND

Exercise. Prove that NOR is a universal gate.

# Logic Design (continued)

#### XOR Revisited

XOR is also called modulo-2 addition.

| Α | В | С | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

$A \oplus B = 1$  only when there are an odd number of 1's in (A,B). The same is true for  $A \oplus B \oplus C$  also.

$$1 \oplus A = \overline{A}$$

$$0 \oplus A = A$$

Why?

# Logic Design Examples

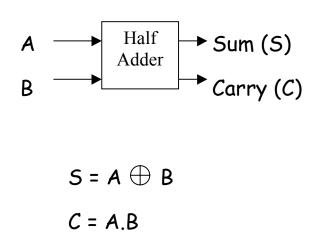

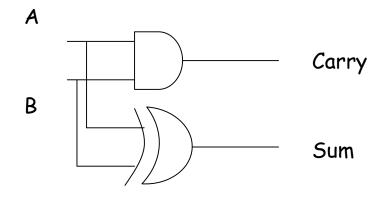

### <u>Half Adder</u>

| Α | В | S | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

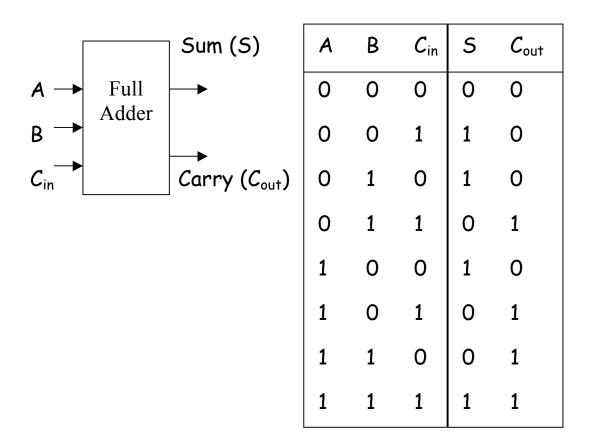

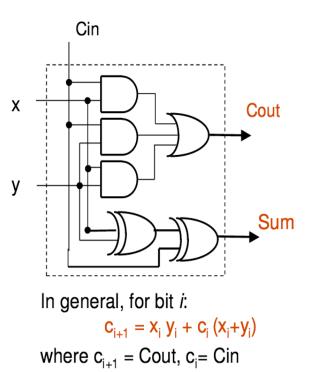

#### Full Adder

$S = A \oplus B \oplus C_{in}$  $C_{out} = A.B + B.C_{in} + A.C_{in}$

Design a full adder using two half-adders (and a few gates if necessary).

2. Can you design a 1-bit subtractor?

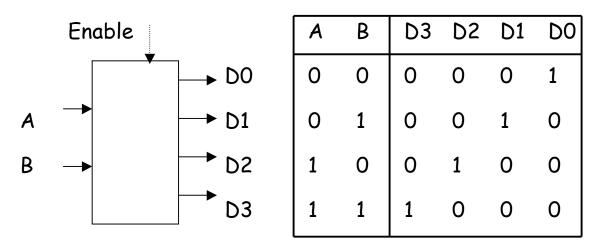

#### Decoders

A typical decoder has n inputs and 2<sup>n</sup> outputs.

A 2-to-4 decoder and its truth table

D3 = A.B D2 = A.B D1 = A.B D0 = A.B

Draw the circuit of this decoder.

The decoder works per specs when (Enable = 1). When Enable = 0,

all the outputs are 0.

Exercise. Design a 3-to-8 decoder.Question. Where are decoders used?Can you design a 2-4 decoder using 1-2 decoders?

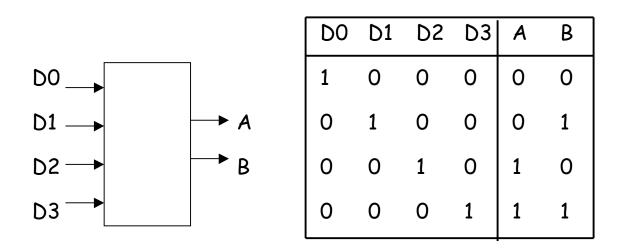

### Encoders

A typical encoder has 2<sup>n</sup> inputs and n outputs.

A 4-to-2 encoder and its truth table

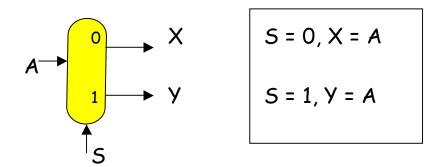

#### <u>Multiplexor</u>

It is a many-to-one switch, also called a selector.

S = 0, F = A S = 1, F = B

Control S

Specifications of the mux

A 2-to-1 mux

Exercise. Design a 4-to-1 multiplexor using two 2-to-1 multiplexors.

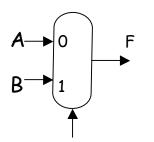

#### **Demultiplexors**

A demux is a one-to-many switch.

A 1-to-2 demux and its specification

**Exercise**. Design a 1-4 demux using 1-2 demux.

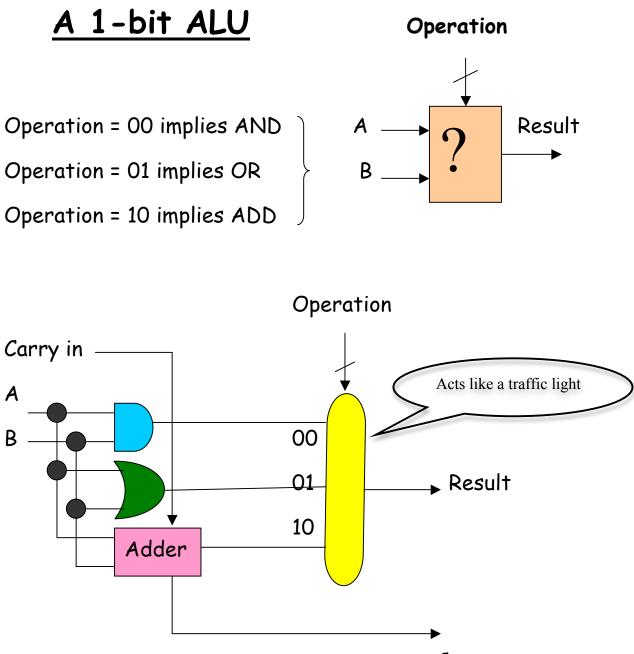

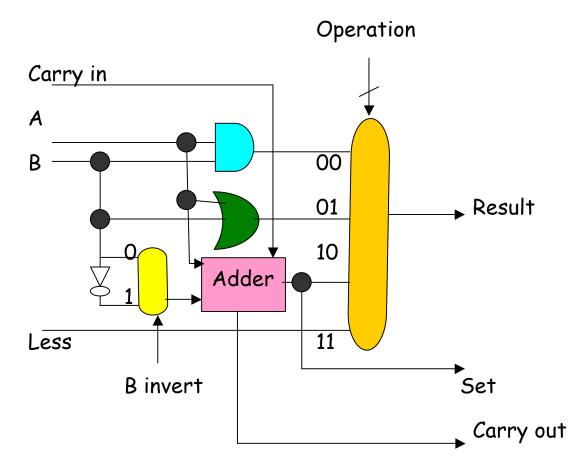

- Carry out

- Understand how this circuit works.

- Let us add one more input to the mux to implement

slt when the Operation = 11

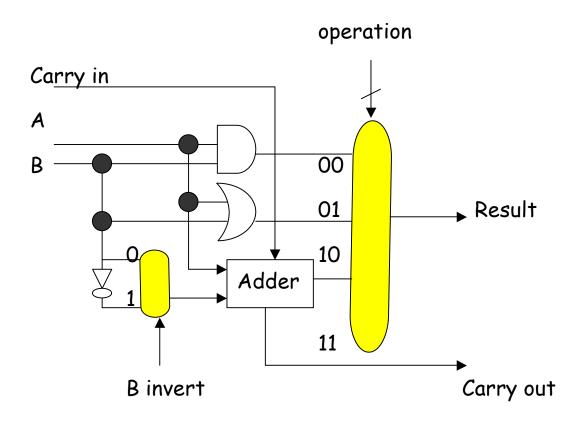

#### Converting an adder into a subtractor

A - B (here - means arithmetic subtraction)

- = A + 2's complement of B

- = A + 1's complement of B + 1

1-bit adder/subtractor

For subtraction, <mark>B invert = 1</mark> and Carry in = 1

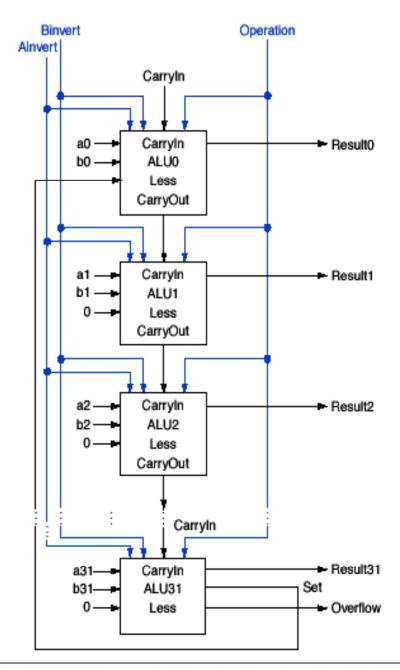

#### 1-bit ALU for MIPS

Assume that it has the instructions add, sub, and, or, slt.

Less = 1 if the 32-bit number A is less than the 32-bit number B. (Its use will be clear from the next page)

We now implement **slt** (If A < B then Set = 1 else Set = 0)

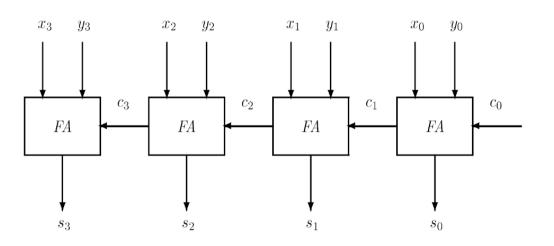

# **Ripple Carry Adder**

- Addition

- most frequent operation

- used also for multiplication and division

- fast two-operand adder essential

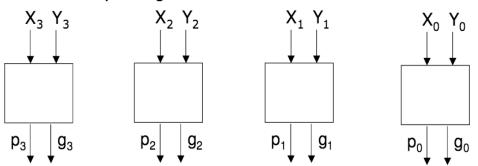

# Simple parallel adder

- for adding Xn-1,Xn-2,...,X0 and Yn-1,Yn-2,...,Y0

- using **n** full adders

- Full adder

- combinational digital circuit with input bits Xi, Yi and incoming carry bit Ci, producing output sum bit Si and outgoing carry bit Ci+1

- incoming carry for next FA with input bits Xi+1, Yi+1

- Si = Xi ⊕ Yi ⊕ Ci

- $C_{i+1} = X_i \cdot Y_i + C_i \cdot (X_i + Y_i)$

# Full-Adder (FA)

Examine the Full Adder table

| х | у | Cin | Cou | t S |

|---|---|-----|-----|-----|

| 0 | 0 | 0   | 0   | 0   |

| 0 | 0 | 1   | 0   | 1   |

| 0 | 1 | 0   | 0   | 1   |

| 0 | 1 | 1   | 1   | 0   |

| 1 | 0 | 0   | 0   | 1   |

| 1 | 0 | 1   | 1   | 0   |

| 1 | 1 | 0   | 1   | 0   |

| 1 | 1 | 1   | 1   | 1   |

Cout =

$$x \cdot y + Cin \cdot (x + y)$$

S =  $x'y'c + x'yc' + xy'c' + xyc$

=  $x \oplus y \oplus c$

# **Parallel Adder: Ripple Carry**

- In a parallel arithmetic unit

- All **2n** input bits available at the same time

- Carry propagates from the FA to the right to FA to the left

- Carries ripple through all **n** FAs before we can claim that the sum outputs are correct and may be used in further calculations

- Each FA has a finite delay

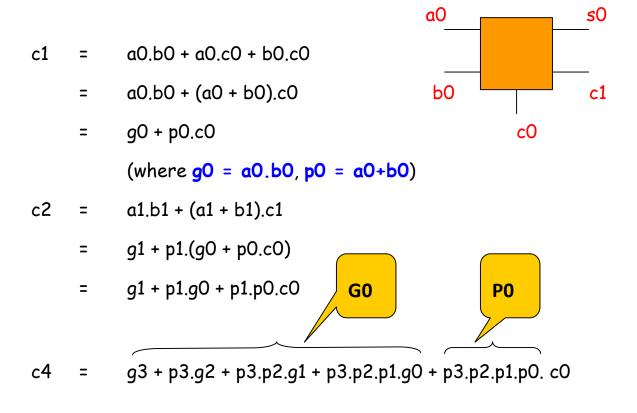

# Fast Carry Propagation; Carry Look Ahead

During addition, the carry can trigger a "ripple" from the

LSB to the MSB. This slows down the speed of addition.

011111111111111111 +

0000000000000000001

Calculate the max time it takes to complete a 32-bit addition if each stage takes 1 ns. How to overcome this? Consider the following:

We could calculate c32 in this way.

# Gates are limited to two inputs

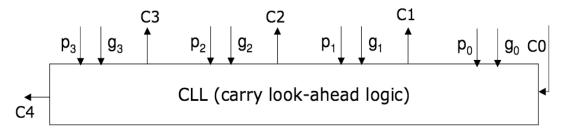

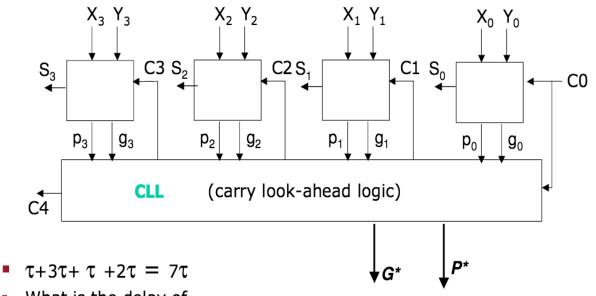

•  $C_4 = g_3 + p_3 g_2 + p_3 p_2 g_1 + p_3 p_2 p_1 g_0 + p_3 p_2 p_1 p_0 c_0$

What if there were 6 inputs? What if there were 7 inputs? What if there were 8 inputs? What if there were 9 inputs? You can always use a two-level circuit to generate c32, which will speed-up addition (do 32-bit addition in 2 ns), but it is impractical due to the complexity.

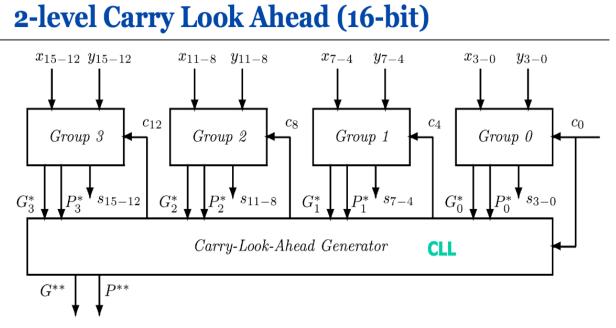

Many practical circuits use a two-phase approach. Consider the example of a 16-bit adder, designed from four 4-bit adders. Let

G0 = g3 + p3.g2 + p3.p2.g1 + p3.p2.p1.g0 G1 = g7 + p7.g6 + p7.p6.g5 + p7.p6.p5.g4 G2 = g11 + p11.g10 + p11.p10.g9 + p11.p10.p9.g8 G3 = g15 + p15.g14 + p15.p14.g13 + p15.p14.p13.g12 P0 = p3.p2.p1.p0 P1 = p7.p6.p5.p4 P2 = p11.p10.p9.p8 P3 = p15.p14.p13.p12

Then if C1, C2, C3, C4 are the output carry bit from the  $1^{st}$ ,  $2^{nd}$ ,  $3^{rd}$ ,  $4^{th}$  4-bit adders, then we can write

C1 = G0 + P0.c0 C2 = G1 + P1.C1 = G1 + P1.G0 + P1.P0.c0 C3 = G2 + P2.C2 = G2 + P2.G1 + P2.P1.G0 + P2.P1.P0.c0 C4 = G3 + P3.C3 = G3 + P3.G2 + P3.P2.G1 + P3.P2.P1.G0 + P3.P2.P1.P0.c0

How does it help? Count the number of levels. The smaller is this number, the faster is the implementation This is implemented in the carry look-ahead adder.

There are other implementations too.

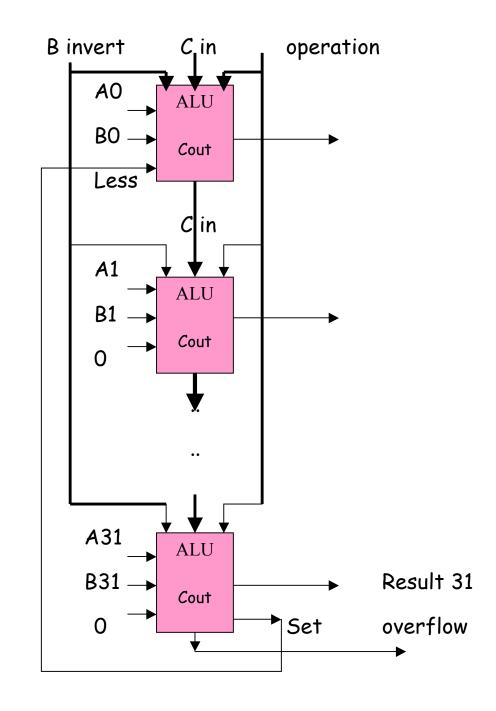

**FIGURE B.5.11** A 32-bit ALU constructed from the 31 copies of the 1-bit ALU in the top of Figure B.5.10 and one 1-bit ALU in the bottom of that figure. The Less inputs are connected to 0 except for the least significant bit, which is connected to the Set output of the most significant bit. If the ALU performs a - b and we select the input 3 in the multiplexor in Figure B.5.10, then Result = 0...001 if a < b, and Result = 0...000 otherwise.

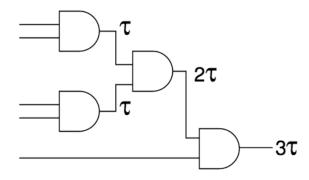

# **Delay of Carry Look Ahead Adders**

Let τ be the delay of a gate

If inputs are available at time t=0, when are p and g signals available?

# **Total Delay**

- What is the delay of a 5 bit CLA?

- 6 bit CLA? 7 bit CLA?

- 8 bit CLA?

$\begin{array}{lll} G^{*} &=& G_{3}+G_{2}P_{3}+G_{1}P_{2}P_{3}+G_{0}P_{1}P_{2}P_{3}\\ P^{*} &=& P_{0}P_{1}P_{2}P_{3}. \end{array}$

n=16 - 4 groups, 4-bit each

$$c_{4} = G_{0}^{*} + c_{0}P_{0}^{*},$$

$$c_{8} = G_{1}^{*} + G_{0}^{*}P_{1}^{*} + c_{0}P_{0}^{*}P_{1}^{*},$$

$$c_{12} = G_{2}^{*} + G_{1}^{*}P_{2}^{*} + G_{0}^{*}P_{1}^{*}P_{2}^{*} + c_{0}P_{0}^{*}P_{1}^{*}P_{2}^{*}$$

### Combinational vs. Sequential Circuits

### **Combinational circuits**

The output depends only on the current values of the inputs and not on the past values. Examples are adders, subtractors, and all the circuits that we have studied so far

### Sequential circuits

The output depends not only on the current values of the inputs, but also on their past values. These hold the secret of how to **memorize information**. We will study sequential circuits later.